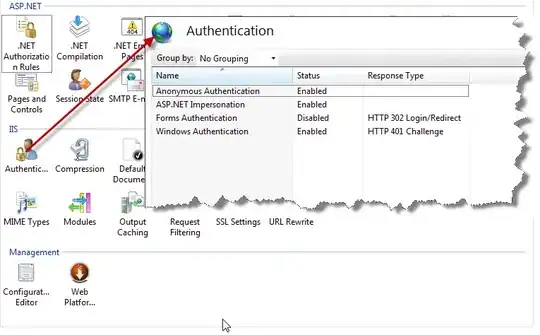

From the speech Herb Sutter in the figure of the slides on page 2: https://skydrive.live.com/view.aspx?resid=4E86B0CF20EF15AD!24884&app=WordPdf&wdo=2&authkey=!AMtj_EflYn2507c

Here are shown separate cache-L1S and Store Buffer (SB).

1. In processors Intel x86 cache-L1 and Store Buffer - is the same thing?

And next slide:

As we see from the next slide in the x86 is only possible following reordering. was:

MOV eax, [memory1] / / read

MOV [memory2], edx / / write

... / / MOV, MFENCE, ADD ... any other code

became:

MOV [memory2], edx / / write

MOV eax, [memory1] / / read

... / / MOV, MFENCE, ADD ... any other code

This is due to the unordered execution in the processor pipeline.

2. But can you show another example similar to this - how does affect on reordering Store Buffer?

3. And the main question - how to influences LFENCE and SFENCE on caches of neighboring cores?

Is correct to say that:

SFENCEmakes "push", ie makes flush for Store Buffer->L1, and then sends changes from the caches of Core0-L1/L2 to all other cores Core1/2/3...-L1/L2?LFENCEmakes "pull", ie receives changes from caches of all other Core1/2/3...-L1/L2( and Store Buffer?) in our core Core0-L1/L2?