I am reading and studying The Elements of Computing Systems but I am stuck at one point. Sample chapter skip the next 5 instruction s can be found here.

Anyway, I am trying to implement a Virtual Machine (or a byte code to assembly translator) but I am stuck at skip the next 5 instruction one point.

You can find the assembly notation here.

The goal is to implement a translator that will translate a specific byte code to this assembly code.

An example I have done successfully is for the byte code

push constant 5

which is translated to:

@5

D=A

@256

M=D

As I said, the assembly language for Hack is found in the link I provided but basically:

@5 // Load constant 5 to Register A

D=A // Assign the value in Reg A to Reg D

@256// Load constant 256 to Register A

M=D // Store the value found in Register D to Memory Location[A]

Well this was pretty straight forward. By definition memory location 256 is the top of the stack. So

push constant 5

push constant 98

will be translated to:

@5

D=A

@256

M=D

@98

D=A

@257

M=D

which is all fine..

I also want to give one more example:

push constant 5

push constant 98

add

is translated to:

@5

D=A

@256

M=D

@98

D=A

@257

M=D

@257 // Here starts the translation for 'add' // Load top of stack to A

D=M // D = M[A]

@256 // Load top of stack to A

A=M // A = M[A]

D=D+A

@256

M=D

I think it is pretty clear.

However I have no idea how I can translate the byte code

eq

to Assembly. Definition for eq is as follows:

Three of the commands (eq, gt, lt) return Boolean values. The VM represents true and false as -1 (minus one, 0xFFFF) and 0 (zero, 0x0000), respectively.

So I need to pop two values to registers A and D respectively, which is quite easy. But how am I supposed to create an Assembly code that will check against the values and push 1 if the result is true or 0 if the result is false?

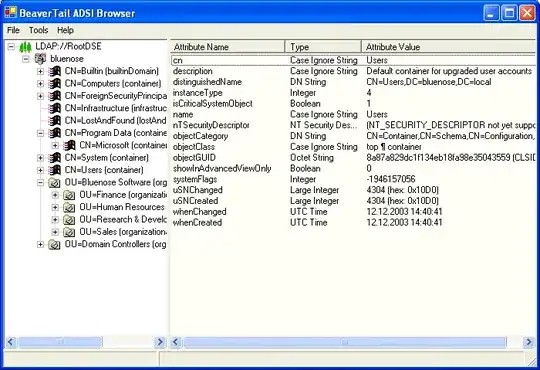

The assembly code supported for Hack Computer is as follows:

I can do something like:

push constant 5

push constant 6

sub

which will hold the value 0 if 2 values pushed to the stack are equal or !0 if not but how does that help? I tried using D&A or D&M but that did not help much either..

I can also introduce a conditional jump but how am I supposed to know what instruction to jump to? Hack Assembly code does not have something like "skip the next 5 instructions" or etc..

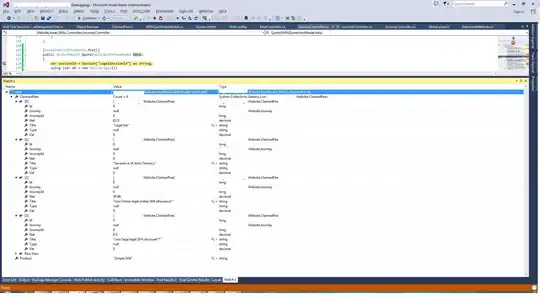

[edit by Spektre] target platform summary as I see it

- 16bit Von Neumann architecture (address is 15 bits with 16 bit Word access)

- Data memory 32KW (Read/Write)

- Instruction (Program) memory 32KW (Read only)

- native 16 bit registers A,D

- general purpose 16 bit registers R0-R15 mapped to Data memory at 0x0000 - 0x000F

- these are most likely used also for:

SP(R0),LCL(R1),ARG(R2),This(R3),That(R4) - Screen is mapped to Data memory at 0x4000-0x5FFF (512x256 B/W pixels 8KW)

- Keyboard is mapped to Data memory at 0x6000 (ASCII code if last hit key?)