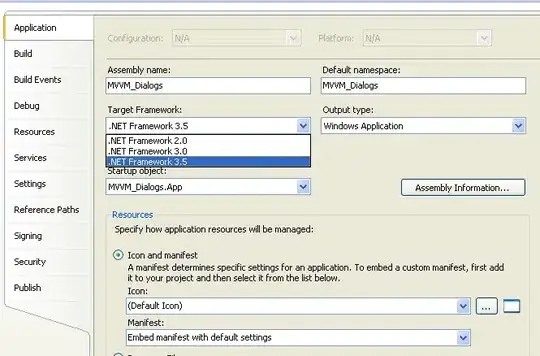

I would not bother trying to understand that diagram because it makes no sense.

It is titled "Paging" but the diagram does not show paging at all.

What you are missing is that there are two steps. First there is logical memory translation (what the diagram kinda, sorta) shows.

Physical memory is arranged in an array of PAGE FRAMES of some fixed size (e.g., 1K, 4K).

Each process has a LOGICAL ADDRESS SPACE consisting of PAGES that match the page frame size.

The logical address space is defined by a PAGE TABLE managed by the operating system. The page table maps logical pages to physical page frames.

If there are two processes (X and Y), logical address Q in process X and address Y map to different physical page frames in most cases.

Usually there is a range of logical addresses that are assigned to the SYSTEM ADDRESS SPACE. Those logical pages map to the same physical page for all processes.

Processes only address logical pages. The have no knowledge of physical pages. The Program Counter register always refers to logical addresses. The CPU automatically translates logical pages to physical page frames. The translation is entirely transparent to the process. The operating system is the only thing that has any knowledge of physical page frame but it only manages the page tables; the CPU does the translation.

Paging is something different but related.

When a program accesses a memory address, the CPU attempts to translate that into a physical address within a page frame. Several steps occur.

The CPU locates the page table entry for the requested page.

There may not be a page page table entry at all for the page. The diagram shows a contiguous logical to physical mapping. That rarely occurs. The logical address space usually has clusters of valid pages with gaps between them. If there is no page table entry for the address, the CPU triggers an exception.

The CPU reads the page table entry to determine if it references a valid page frame.

There may be an entry for the page that has not been mapped to the logical address space (e.g., the first page is usually not mapped to trap null pointer errors). If the page has not been mapped, that triggers an exception.

The CPU checks whether the access is permitted for the current processor mode.

Read/Write/Execute protection can be set for a page and access can be restricted by mode (kernel mode, user mode, or some other mode in some processors).

If the access is not permitted, the CPU triggers an exception.

[Here is where paging comes in] The CPU checks whether the page has been mapped to a physical page frame. If not, the CPU triggers a PAGE FAULT. The OS responds by locating where the page is stored in a paging file, mapping the page table to a physical page frame, loading the data from the page file into memory, and then restarting the instruction.