I have been attempting to get access to GPIO2 and GPIO3 on the beaglebone black through kernel module with no success. Every time I attempt to assign an output value to GPIOs 2 and 3 I get a segmentation fault.

The exact same code (with the appropriate pin assignment) works for GPIO0 and GPIO1.

I have attempted various pins on both P8 and P9 related to GPIO2 and GPIO3 with no success. On the flip side, the same exact code works for GPIO0 and GPIO1 with appropriate pin assignment.

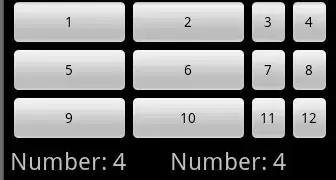

For pin values I am using the official BBB manual. For appropriate I/O GPIO availability I am checking this diagram from beagleboard.com:

#include <linux/init.h>

#include <linux/module.h>

#include <linux/kernel.h>

#include <net/tcp.h>

//Macros

#define GPIO1_START_ADDR 0x4804C000

#define GPIO2_START_ADDR 0x481AC000

#define GPIO2_END_ADDR 0x481ACFFF

#define GPIO3_START_ADDR 0x481AE000

#define SIZE (GPIO2_END_ADDR - GPIO2_START_ADDR)

#define GPIO_OE 0x134

#define GPIO_DATAOUT 0x13C

//A couple of standard descriptions

MODULE_LICENSE("GPL");

static int hello_init(void)

{

volatile void *gpio_addr;

volatile unsigned int *oe_addr;

volatile unsigned int *dataout_addr;

printk(KERN_NOTICE "Module: Initializing module\n");

printk(KERN_NOTICE "Module: Map GPIO\n");

gpio_addr = ioremap(GPIO3_START_ADDR,SIZE);

printk(KERN_NOTICE "Module: Set oe_addr\n");

oe_addr = gpio_addr + GPIO_OE;

printk(KERN_NOTICE "Module: Set dataout_addr\n");

dataout_addr = gpio_addr + GPIO_DATAOUT;

//Code will work up to here for any GPIO.

//It crashes on the following for GPIO2 and GPIO3:

printk(KERN_NOTICE "Module: Set pin to OUTPUT\n");

*oe_addr &= (0xFFFFFFFF ^ (1<<19));

printk(KERN_NOTICE "Module: Set pin output to HIGH\n");

*dataout_addr |= (1<<19);

return 0;

}

static void hello_exit(void)

{

printk(KERN_INFO "Exit module.\n");

}

module_init(hello_init);

module_exit(hello_exit);

If I block out the two lines

*oe_addr &= (0xFFFFFFFF ^ (1<<19)); and

*dataout_addr |= (1<<19);, the program runs for all GPIOs without glitch.

$uname -a: Linux beaglebone 3.8.13-bone79

Why am I getting segmentation fault when accessing GPIO2 and GPIO3?