I am a beginner of assembly language, so I hope anyone who give me a answer could explain be more specific.

Question is converting from C to assembly language.

C code is:

while(save[i] == k)

i += 1;

i and k are in $s3 and $s5 and base of array save[] is in $s6

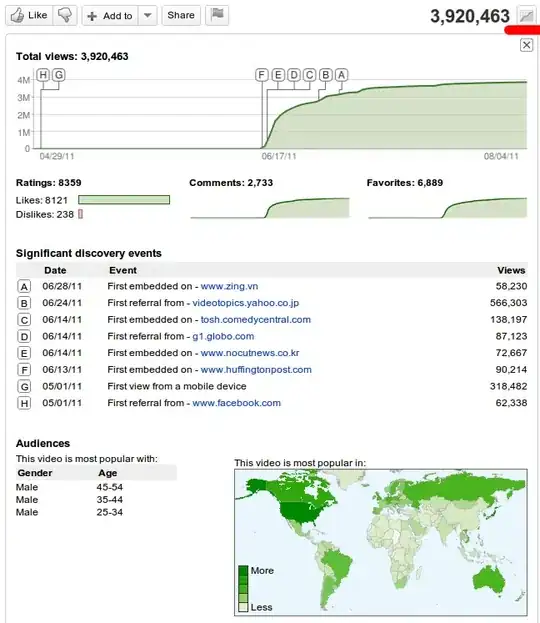

The answer is in the figure.

What I misunderstand is that why $S3 multiple 2^2(==4), and then store into $t1.

I check on stackoverflow for similar questions, some people said "You should add the base and index together, and remember to scale by 4 for the word size. "

But because I am a beginner, I am still confused.

For example,

after a one cycle,

i == 2(in$S3).and then start over,

i == 2in$S3multiple by 4, we get 8 here, and then writes into$t1.

So there is a question, why is 8? I think what we need is save[2] not save[8].

I thought I might confused about value and address.

An another question is: how many bits are those register like $S1, $t1? I think is 32 bits, so it should be 1 word.