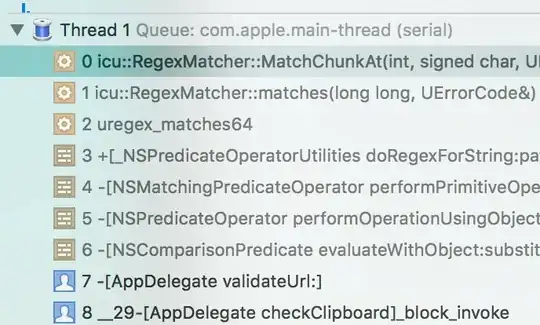

The image is an example of translating in virtual memory. The address of phys. mem. starts from 0x000 ~ 0x0FC, then moves starting 0x100 ~ 0x1FC and so on. Why don't it goes like 0x000 ~ 0x0FF, and then 0x100 ~ 0x1FF etc. What are the two lowest bits stand for?

Asked

Active

Viewed 82 times

1

-

Looks like an error in the table, or else they're assuming that byte / halfword and unaligned accesses are impossible, so it's really a word-addressable machine with 2 unused low bits. (Or for use by software to implement packed 8-bit characters with pointers that software has to pick apart into a word load and a shift by those low two bits. C++11 would forbid a C++ implementation using that for `char*` unless it the RMW RMWs of the containing word for byte stores were atomic, but this might be an old diagram or not trying to be usable for C++11.) – Peter Cordes Oct 05 '22 at 11:51

-

That's a good observation and good question. There's no common or obvious reason why that would be the case. Looks like the authors were thinking in terms of 4-byte words while still considering the system byte-addressable, in the making of that diagram. You'd have to ask them for a definitive answer. – Erik Eidt Oct 05 '22 at 15:21

1 Answers

0

Thank you for your answers. This photo came from MIT open course, and they didn't reveal more details about the address. But I finally figured it out in the later example of the courses.

The two lowest bits can always be zero as the following example:

Suppose that we have:

4GB of MM size.

64 lines of cache.

ONLY 1 WORD = 4 bytes PER CACHE LINE.

The address have 32 bits because of 4GB of MM.

The partial address defining the line have 6 bits because of 64 lines of cache.

And because the cache size is 2^6*4B

=> The tag have 24 bits (log2(4GB/2^8B))

=> The lowest bits have 2(32 - 24 - 6) bits.

Because there is only a word per block so that the lowest bits, which act as a data boundary(This is what the course said), are always 0.

Tony Cheng

- 11

- 2

-

Yes, the address of any aligned 32-bit word has the low 2 bits being zero. But most machines also support single-byte load & store from any address, even if they only support aligned words. (e.g. MIPS `lb` instead of `lw`.) Otherwise you have a machine like DEC Alpha, which had byte-addressable memory, but only 32 and 64-bit load/store instructions. (Until a couple generations later.) See also [Can modern x86 hardware not store a single byte to memory?](https://stackoverflow.com/q/46721075). – Peter Cordes Oct 09 '22 at 19:46