I'm working on this practice question 5.5 in the textbook:

Randal E. Bryant, David R. O’Hallaron - Computer Systems. A Programmer’s Perspective [3rd ed.] (2016, Pearson).

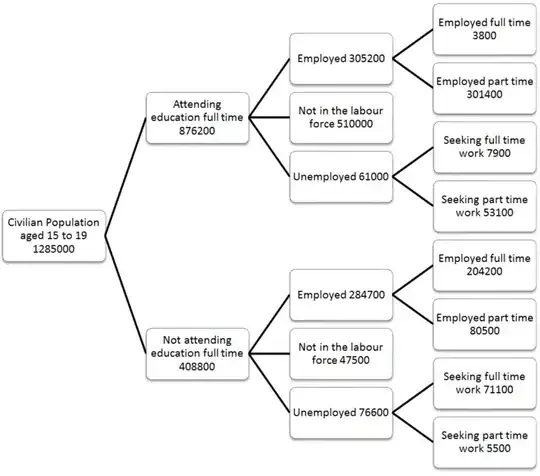

Here is the problem description:

In B, my idea is that CPE for this func is 8n because the performance-limiting computation is result, which requires floating point mul and floating point add. However, the solution says it's 5n due to xpwr=x * xpwr.

Can someone help explain what's wrong in my idea?

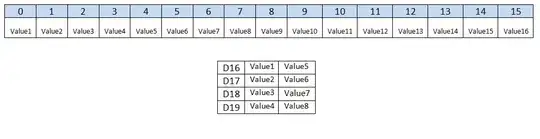

This is the data-flow I drew.