In 'Patterson and Hennessy, Computer Architecture: A Quantitative Approach' 6th ed book p136, it has the following sentences:

The page frame of the instruction’s address (36 = 48 - 12 bits) is sent to the instruction TLB (step 1). At the same time, the 12-bit page offset from the vir- tual address is sent to the instruction cache (step 2).Notice that for the eight-way associative instruction cache, 12 bits are needed for the cache address: 6 bits to index the cache plus 6 bits of block offset for the 64-byte block, so no aliases are possible.The previous versions of the i7 used a four-way set associative I-cache, meaning that a block corresponding to a virtual address could actually be in two different places in the cache, because the corresponding physical address could have either a 0 or 1 in this location. For instructions this did not pose a prob- lem because even if an instruction appeared in the cache in two different locations, the two versions must be the same. If such duplication, or aliasing, of data is allowed, the cache must be checked when the page map is changed, which is an infrequent event. Note that a very simple use of page coloring (see Appendix B, Section B.3) can eliminate the possibility of these aliases. If even-address virtual pages are mapped to even-address physical pages (and the same for odd pages), then these aliases can never occur because the low-order bit in the virtual and phys- ical page number will be identical.

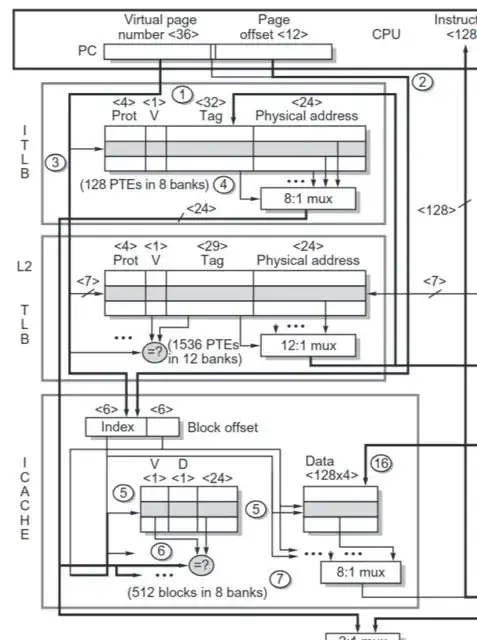

part of 'Figure 2.25 The Intel i7 memory hierarchy and the steps in both instruction and data access.' from the book:

Q:

1.1 questions about the meaning of some sentences above:

Here 'four-way set associative' will not imply the stored data. So what does 'corresponding physical address could have either a 0 or 1 in this location' mean ? where is the 'location'?

Does 'a block corresponding to a virtual address' means the data block stored in the physical address mapped from the virtual address ?

1.2 From above, it seems that the 'four-way set associative' causes the 'alias'. But from this Q&A, I think it is the different mapping ('page map' in the above quote) that causes the alias. So how does 'four-way set associative' cause that 'a block corresponding to a virtual address could actually be in two different places in the cache'?