According to MSDN documentation and Stephen Toub answer, my C# app should use every Logical Processor of every Processor Group because it is configured as required (see my App.config below).

I run my app on a windows server 2012 with a NUMA architecture: 2 x [cpu Xeon E5-2697 v3 at 14 cores each with Hyper Thread activated] => 2 x 14 x 2 = 56 Logical Processors.

My app start 80 threads either from "Thread Class" or "Parallel.For" and in both case it only takes 28 Logical Processors, all from the same Processor Group.

Why does the Task scheduler assign my threads on only one Processor Group?

My code is available at GitHub or the executable could be downloaded at my Home website

I've already asked this question on social.msdn.microsoft.com without any answers.

Update 2015-01-26: I reported a bug at connect.microsoft.com

Update 2015-01-30: I added CoreInfo dump as additional references.

Update 2015-01-30: The problem occurs also with prime95 where it only offer to select 28 threads (not c# related)

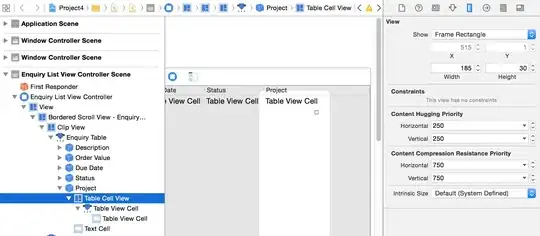

Update 2015-01-30: My tool now show more information like Processor Mask per node. It sounds like I do not have access to the other node (the node I do not run in)

Update 2015-02-02, We do NOT have Citrix installed on this particular server (sorry, I was wrong)

Update 2015-02-02, We contacted HP...

Update 2015-02-03, Added more information to my program to display processorGroup per thread and few more little gadgets.

Update 2015-02-17, After talked to HP dev team, I updated my answer to reflect what I learned. (Just want to mention that I received EXCELLENT support from HP)

Update 2015-05-13, HP confirmed the problem in a "Customer Advisory" note. See this linked document id: c04650594

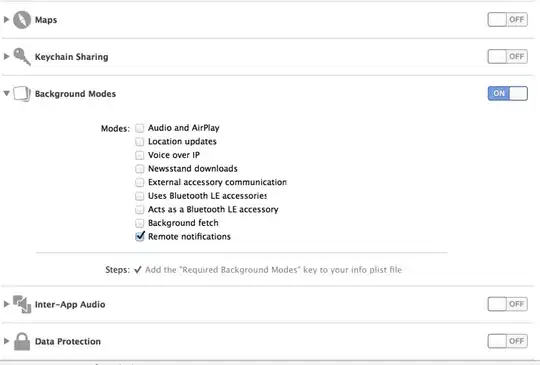

I set my .Net 4.5 (or 4.5.1) App.Config to:

<?xml version="1.0" encoding="utf-8"?>

<configuration>

<runtime>

<Thread_UseAllCpuGroups enabled="true"></Thread_UseAllCpuGroups>

<GCCpuGroup enabled="true"></GCCpuGroup>

<gcServer enabled="true"></gcServer>

</runtime>

<startup>

<supportedRuntime version="v4.0" sku=".NETFramework,Version=v4.5.1"/>

</startup>

</configuration>

This is the dump of CoreInfo from Microsoft:

Intel(R) Xeon(R) CPU E5-2697 v3 @ 2.60GHz

Intel64 Family 6 Model 63 Stepping 2, GenuineIntel

Microcode signature: 00000023

HTT * Hyperthreading enabled

HYPERVISOR - Hypervisor is present

VMX * Supports Intel hardware-assisted virtualization

SVM - Supports AMD hardware-assisted virtualization

X64 * Supports 64-bit mode

SMX * Supports Intel trusted execution

SKINIT - Supports AMD SKINIT

NX * Supports no-execute page protection

SMEP * Supports Supervisor Mode Execution Prevention

SMAP - Supports Supervisor Mode Access Prevention

PAGE1GB * Supports 1 GB large pages

PAE * Supports > 32-bit physical addresses

PAT * Supports Page Attribute Table

PSE * Supports 4 MB pages

PSE36 * Supports > 32-bit address 4 MB pages

PGE * Supports global bit in page tables

SS * Supports bus snooping for cache operations

VME * Supports Virtual-8086 mode

RDWRFSGSBASE * Supports direct GS/FS base access

FPU * Implements i387 floating point instructions

MMX * Supports MMX instruction set

MMXEXT - Implements AMD MMX extensions

3DNOW - Supports 3DNow! instructions

3DNOWEXT - Supports 3DNow! extension instructions

SSE * Supports Streaming SIMD Extensions

SSE2 * Supports Streaming SIMD Extensions 2

SSE3 * Supports Streaming SIMD Extensions 3

SSSE3 * Supports Supplemental SIMD Extensions 3

SSE4a - Supports Streaming SIMDR Extensions 4a

SSE4.1 * Supports Streaming SIMD Extensions 4.1

SSE4.2 * Supports Streaming SIMD Extensions 4.2

AES * Supports AES extensions

AVX * Supports AVX intruction extensions

FMA * Supports FMA extensions using YMM state

MSR * Implements RDMSR/WRMSR instructions

MTRR * Supports Memory Type Range Registers

XSAVE * Supports XSAVE/XRSTOR instructions

OSXSAVE * Supports XSETBV/XGETBV instructions

RDRAND * Supports RDRAND instruction

RDSEED - Supports RDSEED instruction

CMOV * Supports CMOVcc instruction

CLFSH * Supports CLFLUSH instruction

CX8 * Supports compare and exchange 8-byte instructions

CX16 * Supports CMPXCHG16B instruction

BMI1 * Supports bit manipulation extensions 1

BMI2 * Supports bit manipulation extensions 2

ADX - Supports ADCX/ADOX instructions

DCA * Supports prefetch from memory-mapped device

F16C * Supports half-precision instruction

FXSR * Supports FXSAVE/FXSTOR instructions

FFXSR - Supports optimized FXSAVE/FSRSTOR instruction

MONITOR * Supports MONITOR and MWAIT instructions

MOVBE * Supports MOVBE instruction

ERMSB * Supports Enhanced REP MOVSB/STOSB

PCLMULDQ * Supports PCLMULDQ instruction

POPCNT * Supports POPCNT instruction

LZCNT * Supports LZCNT instruction

SEP * Supports fast system call instructions

LAHF-SAHF * Supports LAHF/SAHF instructions in 64-bit mode

HLE - Supports Hardware Lock Elision instructions

RTM - Supports Restricted Transactional Memory instructions

DE * Supports I/O breakpoints including CR4.DE

DTES64 * Can write history of 64-bit branch addresses

DS * Implements memory-resident debug buffer

DS-CPL * Supports Debug Store feature with CPL

PCID * Supports PCIDs and settable CR4.PCIDE

INVPCID * Supports INVPCID instruction

PDCM * Supports Performance Capabilities MSR

RDTSCP * Supports RDTSCP instruction

TSC * Supports RDTSC instruction

TSC-DEADLINE * Local APIC supports one-shot deadline timer

TSC-INVARIANT * TSC runs at constant rate

xTPR * Supports disabling task priority messages

EIST * Supports Enhanced Intel Speedstep

ACPI * Implements MSR for power management

TM * Implements thermal monitor circuitry

TM2 * Implements Thermal Monitor 2 control

APIC * Implements software-accessible local APIC

x2APIC * Supports x2APIC

CNXT-ID - L1 data cache mode adaptive or BIOS

MCE * Supports Machine Check, INT18 and CR4.MCE

MCA * Implements Machine Check Architecture

PBE * Supports use of FERR#/PBE# pin

PSN - Implements 96-bit processor serial number

PREFETCHW * Supports PREFETCHW instruction

Maximum implemented CPUID leaves: 0000000F (Basic), 80000008 (Extended).

Logical to Physical Processor Map:

Physical Processor 0 (Hyperthreaded):

**------------------------------------------------------

Physical Processor 1 (Hyperthreaded):

--**----------------------------------------------------

Physical Processor 2 (Hyperthreaded):

----**--------------------------------------------------

Physical Processor 3 (Hyperthreaded):

------**------------------------------------------------

Physical Processor 4 (Hyperthreaded):

--------**----------------------------------------------

Physical Processor 5 (Hyperthreaded):

----------**--------------------------------------------

Physical Processor 6 (Hyperthreaded):

------------**------------------------------------------

Physical Processor 7 (Hyperthreaded):

--------------**----------------------------------------

Physical Processor 8 (Hyperthreaded):

----------------**--------------------------------------

Physical Processor 9 (Hyperthreaded):

------------------**------------------------------------

Physical Processor 10 (Hyperthreaded):

--------------------**----------------------------------

Physical Processor 11 (Hyperthreaded):

----------------------**--------------------------------

Physical Processor 12 (Hyperthreaded):

------------------------**------------------------------

Physical Processor 13 (Hyperthreaded):

--------------------------**----------------------------

Physical Processor 14 (Hyperthreaded):

----------------------------**--------------------------

Physical Processor 15 (Hyperthreaded):

------------------------------**------------------------

Physical Processor 16 (Hyperthreaded):

--------------------------------**----------------------

Physical Processor 17 (Hyperthreaded):

----------------------------------**--------------------

Physical Processor 18 (Hyperthreaded):

------------------------------------**------------------

Physical Processor 19 (Hyperthreaded):

--------------------------------------**----------------

Physical Processor 20 (Hyperthreaded):

----------------------------------------**--------------

Physical Processor 21 (Hyperthreaded):

------------------------------------------**------------

Physical Processor 22 (Hyperthreaded):

--------------------------------------------**----------

Physical Processor 23 (Hyperthreaded):

----------------------------------------------**--------

Physical Processor 24 (Hyperthreaded):

------------------------------------------------**------

Physical Processor 25 (Hyperthreaded):

--------------------------------------------------**----

Physical Processor 26 (Hyperthreaded):

----------------------------------------------------**--

Physical Processor 27 (Hyperthreaded):

------------------------------------------------------**

Logical Processor to Socket Map:

Socket 0:

****************************----------------------------

Socket 1:

----------------------------****************************

Logical Processor to NUMA Node Map:

NUMA Node 0:

****************************----------------------------

NUMA Node 1:

----------------------------****************************

Calculating Cross-NUMA Node Access Cost...

Approximate Cross-NUMA Node Access Cost (relative to fastest):

00 01

00: 1.0 1.1

01: 1.1 1.1

Logical Processor to Cache Map:

Data Cache 0, Level 1, 32 KB, Assoc 8, LineSize 64

**------------------------------------------------------

Instruction Cache 0, Level 1, 32 KB, Assoc 8, LineSize 64

**------------------------------------------------------

Unified Cache 0, Level 2, 256 KB, Assoc 8, LineSize 64

**------------------------------------------------------

Unified Cache 1, Level 3, 35 MB, Assoc 20, LineSize 64

****************************----------------------------

Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--**----------------------------------------------------

Instruction Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64

--**----------------------------------------------------

Unified Cache 2, Level 2, 256 KB, Assoc 8, LineSize 64

--**----------------------------------------------------

Data Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

----**--------------------------------------------------

Instruction Cache 2, Level 1, 32 KB, Assoc 8, LineSize 64

----**--------------------------------------------------

Unified Cache 3, Level 2, 256 KB, Assoc 8, LineSize 64

----**--------------------------------------------------

Data Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

------**------------------------------------------------

Instruction Cache 3, Level 1, 32 KB, Assoc 8, LineSize 64

------**------------------------------------------------

Unified Cache 4, Level 2, 256 KB, Assoc 8, LineSize 64

------**------------------------------------------------

Data Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

--------**----------------------------------------------

Instruction Cache 4, Level 1, 32 KB, Assoc 8, LineSize 64

--------**----------------------------------------------

Unified Cache 5, Level 2, 256 KB, Assoc 8, LineSize 64

--------**----------------------------------------------

Data Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

----------**--------------------------------------------

Instruction Cache 5, Level 1, 32 KB, Assoc 8, LineSize 64

----------**--------------------------------------------

Unified Cache 6, Level 2, 256 KB, Assoc 8, LineSize 64

----------**--------------------------------------------

Data Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

------------**------------------------------------------

Instruction Cache 6, Level 1, 32 KB, Assoc 8, LineSize 64

------------**------------------------------------------

Unified Cache 7, Level 2, 256 KB, Assoc 8, LineSize 64

------------**------------------------------------------

Data Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------------**----------------------------------------

Instruction Cache 7, Level 1, 32 KB, Assoc 8, LineSize 64

--------------**----------------------------------------

Unified Cache 8, Level 2, 256 KB, Assoc 8, LineSize 64

--------------**----------------------------------------

Data Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

----------------**--------------------------------------

Instruction Cache 8, Level 1, 32 KB, Assoc 8, LineSize 64

----------------**--------------------------------------

Unified Cache 9, Level 2, 256 KB, Assoc 8, LineSize 64

----------------**--------------------------------------

Data Cache 9, Level 1, 32 KB, Assoc 8, LineSize 64

------------------**------------------------------------

Instruction Cache 9, Level 1, 32 KB, Assoc 8, LineSize 64

------------------**------------------------------------

Unified Cache 10, Level 2, 256 KB, Assoc 8, LineSize 64

------------------**------------------------------------

Data Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------**----------------------------------

Instruction Cache 10, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------**----------------------------------

Unified Cache 11, Level 2, 256 KB, Assoc 8, LineSize 64

--------------------**----------------------------------

Data Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------**--------------------------------

Instruction Cache 11, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------**--------------------------------

Unified Cache 12, Level 2, 256 KB, Assoc 8, LineSize 64

----------------------**--------------------------------

Data Cache 12, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------**------------------------------

Instruction Cache 12, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------**------------------------------

Unified Cache 13, Level 2, 256 KB, Assoc 8, LineSize 64

------------------------**------------------------------

Data Cache 13, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------**----------------------------

Instruction Cache 13, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------**----------------------------

Unified Cache 14, Level 2, 256 KB, Assoc 8, LineSize 64

--------------------------**----------------------------

Data Cache 14, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------**--------------------------

Instruction Cache 14, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------**--------------------------

Unified Cache 15, Level 2, 256 KB, Assoc 8, LineSize 64

----------------------------**--------------------------

Unified Cache 16, Level 3, 35 MB, Assoc 20, LineSize 64

----------------------------****************************

Data Cache 15, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------**------------------------

Instruction Cache 15, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------**------------------------

Unified Cache 17, Level 2, 256 KB, Assoc 8, LineSize 64

------------------------------**------------------------

Data Cache 16, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------**----------------------

Instruction Cache 16, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------**----------------------

Unified Cache 18, Level 2, 256 KB, Assoc 8, LineSize 64

--------------------------------**----------------------

Data Cache 17, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------**--------------------

Instruction Cache 17, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------**--------------------

Unified Cache 19, Level 2, 256 KB, Assoc 8, LineSize 64

----------------------------------**--------------------

Data Cache 18, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------**------------------

Instruction Cache 18, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------**------------------

Unified Cache 20, Level 2, 256 KB, Assoc 8, LineSize 64

------------------------------------**------------------

Data Cache 19, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------------**----------------

Instruction Cache 19, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------------**----------------

Unified Cache 21, Level 2, 256 KB, Assoc 8, LineSize 64

--------------------------------------**----------------

Data Cache 20, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------------**--------------

Instruction Cache 20, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------------**--------------

Unified Cache 22, Level 2, 256 KB, Assoc 8, LineSize 64

----------------------------------------**--------------

Data Cache 21, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------------**------------

Instruction Cache 21, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------------**------------

Unified Cache 23, Level 2, 256 KB, Assoc 8, LineSize 64

------------------------------------------**------------

Data Cache 22, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------------------**----------

Instruction Cache 22, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------------------**----------

Unified Cache 24, Level 2, 256 KB, Assoc 8, LineSize 64

--------------------------------------------**----------

Data Cache 23, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------------------**--------

Instruction Cache 23, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------------------**--------

Unified Cache 25, Level 2, 256 KB, Assoc 8, LineSize 64

----------------------------------------------**--------

Data Cache 24, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------------------**------

Instruction Cache 24, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------------------**------

Unified Cache 26, Level 2, 256 KB, Assoc 8, LineSize 64

------------------------------------------------**------

Data Cache 25, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------------------------**----

Instruction Cache 25, Level 1, 32 KB, Assoc 8, LineSize 64

--------------------------------------------------**----

Unified Cache 27, Level 2, 256 KB, Assoc 8, LineSize 64

--------------------------------------------------**----

Data Cache 26, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------------------------**--

Instruction Cache 26, Level 1, 32 KB, Assoc 8, LineSize 64

----------------------------------------------------**--

Unified Cache 28, Level 2, 256 KB, Assoc 8, LineSize 64

----------------------------------------------------**--

Data Cache 27, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------------------------**

Instruction Cache 27, Level 1, 32 KB, Assoc 8, LineSize 64

------------------------------------------------------**

Unified Cache 29, Level 2, 256 KB, Assoc 8, LineSize 64

------------------------------------------------------**

Logical Processor to Group Map:

Group 0:

****************************----------------------------

Group 1:

----------------------------****************************

This is the MsInfo32 command dump (information about the server):

OS Name Microsoft Windows Server 2012 R2 Standard

Version 6.3.9600 Build 9600

Other OS Description Not Available

OS Manufacturer Microsoft Corporation

System Name EMTP6

System Manufacturer HP

System Model ProLiant DL360 Gen9

System Type x64-based PC

System SKU 755258-B21

Processor Intel(R) Xeon(R) CPU E5-2697 v3 @ 2.60GHz, 2597 Mhz, 14 Core(s), 28 Logical Processor(s)

Processor Intel(R) Xeon(R) CPU E5-2697 v3 @ 2.60GHz, 2597 Mhz, 14 Core(s), 28 Logical Processor(s)

BIOS Version/Date HP P89, 7/11/2014

SMBIOS Version 2.8

Embedded Controller Version 2.02

BIOS Mode UEFI

Platform Role Enterprise Server

Secure Boot State Off

PCR7 Configuration Not Available

Windows Directory ---removed

System Directory ---removed

Boot Device \Device\HarddiskVolume2

Locale United States

Hardware Abstraction Layer Version = "6.3.9600.17196"

User Name Not Available

Time Zone Eastern Standard Time

Installed Physical Memory (RAM) 256 GB

Total Physical Memory 256 GB

Available Physical Memory 246 GB

Total Virtual Memory 294 GB

Available Virtual Memory 283 GB

Page File Space 38.0 GB

Page File ---removed

Hyper-V - VM Monitor Mode Extensions Yes

Hyper-V - Second Level Address Translation Extensions Yes

Hyper-V - Virtualization Enabled in Firmware Yes

Hyper-V - Data Execution Protection Yes

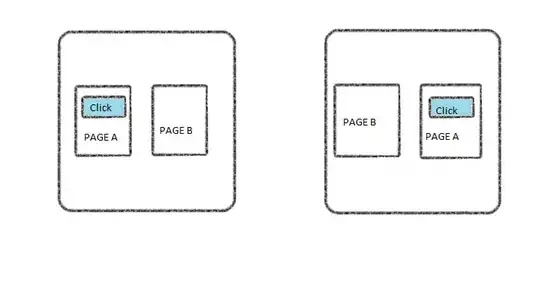

This is the screen shot of TaskManager and my program results:

Or, if Windows decided to start it on node 1:

Expected behavior from another Server:

OS Name Microsoft Windows Server 2008 HPC Edition

Version 6.1.7601 Service Pack 1 Build 7601

Other OS Description Not Available

OS Manufacturer Microsoft Corporation

System Name COMPUTE-13-6

System Manufacturer HP

System Model ProLiant DL160 G6

System Type x64-based PC

Processor Intel(R) Xeon(R) CPU X5675 @ 3.07GHz, 3068 Mhz, 6 Core(s), 6 Logical Processor(s)

Processor Intel(R) Xeon(R) CPU X5675 @ 3.07GHz, 3068 Mhz, 6 Core(s), 6 Logical Processor(s)

BIOS Version/Date HP O33, 7/1/2013

SMBIOS Version 2.7

Windows Directory C:\Windows

System Directory C:\Windows\system32

Boot Device \Device\HarddiskVolume1

Locale United States

Hardware Abstraction Layer Version = "6.1.7601.17514"

User Name Not Available

Time Zone Eastern Standard Time

Installed Physical Memory (RAM) 48.0 GB

Total Physical Memory 48.0 GB

Available Physical Memory 40.9 GB

Total Virtual Memory 96.0 GB

Available Virtual Memory 88.4 GB

Page File Space 48.0 GB

Page File C:\pagefile.sys

Note: I thought we fixed the problem by changing "Interleaved Memory" parameter in the bios. But i gives us weird results. According to Microsoft Technet we set back the BIOS setting to "NON-Interleaved memory"** (which is required by the OS to see the system as NUMA).