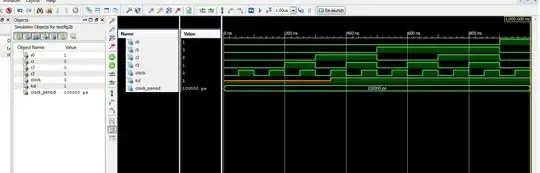

Hi I am a new Xilinx user and been having trouble with how to write stimulus/simulate in a test bench. My output(Kd) isn't giving me any sensible values and gives 'u' for the first few clock cycles before moving and staying at '1' throughout.

Not sure if I have written the correct stimulus but hoping someone would help me out here!

My VHDL code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity codeFig2b is

Port ( R0 : in STD_LOGIC;

R1 : in STD_LOGIC;

R2 : in STD_LOGIC;

R3 : in STD_LOGIC;

Kd : out STD_LOGIC;

clock : in STD_LOGIC);

end codeFig2b;

architecture Behavioral of codeFig2b is

signal Qa, Qb: STD_LOGIC;

begin

process(clock, R0, R1, R2, R3)

begin

if clock = '1' and clock'event then

Qa <= (R0 or R1 or R2 or R3) or (Qa and Qb);

Qb <= Qa;

end if;

end process;

Kd <= Qa and Qb;

end Behavioral;

My Testbench ##

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY codeFig2b_test IS

END codeFig2b_test;

ARCHITECTURE behavior OF codeFig2b_test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT codeFig2b

PORT(

R0 : IN std_logic;

R1 : IN std_logic;

R2 : IN std_logic;

R3 : IN std_logic;

Kd : OUT std_logic;

clock : IN std_logic

);

END COMPONENT;

--Inputs

signal R0 : std_logic := '0';

signal R1 : std_logic := '0';

signal R2 : std_logic := '0';

signal R3 : std_logic := '0';

signal clock : std_logic := '0';

--Outputs

signal Kd : std_logic;

-- Clock period definitions

constant clock_period : time := 100 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: codeFig2b PORT MAP (

R0 => R0,

R1 => R1,

R2 => R2,

R3 => R3,

Kd => Kd,

clock => clock

);

-- Clock process definitions

clock_process :process

begin

clock <= '0';

wait for clock_period/2;

clock <= '1';

wait for clock_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

R0 <= '0';

R1 <= '0';

R2 <= '0';

R3 <= '0';

wait for 100 ns;

R0 <= '0';

R1 <= '0';

R2 <= '0';

R3 <= '1';

wait for 100 ns;

R0 <= '0';

R1 <= '0';

R2 <= '1';

R3 <= '0';

wait for 100 ns;

R0 <= '0';

R1 <= '0';

R2 <= '1';

R3 <= '1';

wait for 100 ns;

R0 <= '0';

R1 <= '1';

R2 <= '0';

R3 <= '0';

wait for 100 ns;

R0 <= '0';

R1 <= '1';

R2 <= '0';

R3 <= '1';

wait for 100 ns;

R0 <= '0';

R1 <= '1';

R2 <= '1';

R3 <= '0';

wait for 100 ns;

R0 <= '0';

R1 <= '1';

R2 <= '1';

R3 <= '1';

wait for 100 ns;

R0 <= '1';

R1 <= '0';

R2 <= '0';

R3 <= '0';

wait for 100 ns;

R0 <= '1';

R1 <= '0';

R2 <= '0';

R3 <= '1';

wait for 100 ns;

R0 <= '1';

R1 <= '0';

R2 <= '1';

R3 <= '0';

wait for 100 ns;

R0 <= '1';

R1 <= '0';

R2 <= '1';

R3 <= '1';

wait for 100 ns;

R0 <= '1';

R1 <= '1';

R2 <= '0';

R3 <= '0';

wait for 100 ns;

R0 <= '1';

R1 <= '1';

R2 <= '0';

R3 <= '1';

wait for 100 ns;

R0 <= '1';

R1 <= '1';

R2 <= '1';

R3 <= '0';

wait for 100 ns;

R0 <= '1';

R1 <= '1';

R2 <= '1';

R3 <= '1';

wait for clock_period*10;

-- insert stimulus here

wait;

end process;

END;