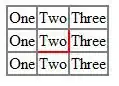

I expected signal 'delay' to be one clock cycle late wrt to the entities' port 'input', but ISIM shows no phase shift. I thought there is always is a delay between signal assignment and actual value (when the process suspends), but I don't seee it here.

Why is this?

Code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity test is

Port ( clk: in std_logic;

input: in std_logic

);

end test;

architecture Behavioral of test is

signal delay: std_logic:= '0';

begin

proc1: process(clk)

begin

if(rising_edge(clk)) then

delay <= input; -- ISIM shows no delay between them

end if;

end process;

end Behavioral;

Testbench:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY tb_testbench_test IS

END tb_testbench_test;

ARCHITECTURE behavior OF tb_testbench_test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT test

PORT(

clk: in std_logic;

input: in std_logic

);

END COMPONENT;

--Inputs

signal clk: std_logic := '0';

signal input: std_logic := '0';

-- Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: test PORT MAP (

clk => clk,

input => input

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

wait for clk_period * 9.5;

input <= '1';

wait for clk_period;

input <= '0';

wait;

end process;

end;