I'm an amateur when it comes to VHDL and hardware in general but I've been working on a project for school and I came across something that I can't understand.

I have a register (type D FF) that's processing a clock signal to store the input value and, in simulation, it works fine if I use a "Force clock" in it's clk input but if I try to "simulate" a clock by manually changing it with "Force Constant" from zero to one and so forth it doesn't "pick up" on the rising edge.

Is this normal behavior? I assumed it would still detect the rising edge when going from 0 to 1.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity register_D is

generic (

WIDTH : POSITIVE := 1

);

Port ( CLK : in STD_LOGIC;

RST : in STD_LOGIC;

EN : in STD_LOGIC;

D : in STD_LOGIC_VECTOR(WIDTH-1 downto 0);

Q : out STD_LOGIC_VECTOR(WIDTH-1 downto 0));

end register_D;

architecture Behavioral of register_D is

begin

process (CLK, RST, EN)

begin

if (RST='1') then

Q <= (others=>'0');

elsif (rising_edge(CLK) and EN = '1') then

Q <= D;

end if;

end process;

end Behavioral;

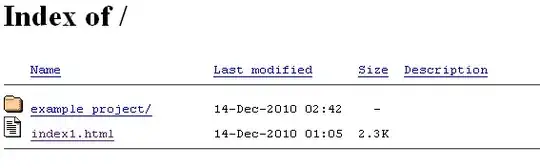

Screenshot of me trying to trigger the FF by manually setting the clock (and not working):

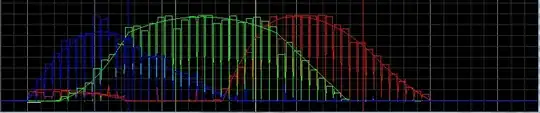

Here you can see it working when I switch clk from "Force constant" to "Force clock":