I am making an FSM with VHDL. The simplest possible when valid = 1 change from stateA to stateB.

I am making an FSM with VHDL. The simplest possible when valid = 1 change from stateA to stateB.

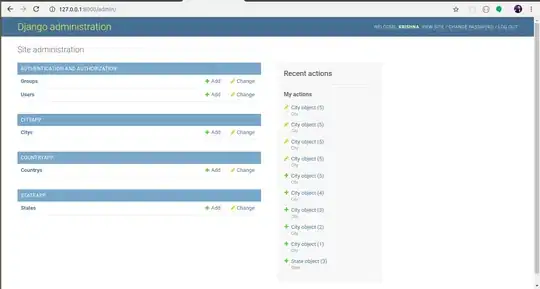

The confusing part is the rising edge selected by the blue rectangular. When valid = '1'. At the first rising edge, the state will be calculated to be B but it won't take effect until the next rising edge BUT what happened that it took effect at the FIRST rising edge.

Because the change in the state from A to B should affect other parts ( parallel process ) in the design in the NEXT cycle. From the waveform, If valid = '1' just before CLK_1.

At, CLK_1 all other processes should see state = A | waveform correct output

- state = A

- enteredlastcycle = 0

At, CLK_2 all processes start seeing state = B. another parallel process checks if state = B then it drives ENTERED_STATEB_LASTCYCLE to be 1 waveform correct output

- state = B

- enteredlastcycle = 0

Then at CLK_3, waveform correct output

- state = B

- enteredlastcycle = 1

Do I misunderstand something?

Library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

use work.KDlib.all;

entity nearestPoint is

generic ( ARRAY_WIDTH : integer := 8);

port (

clk: in std_logic;

reset: in std_logic;

inpoint: in kdvector;

valid: in std_logic;

finished: buffer std_logic

);

end nearestPoint;

architecture behave of nearestPoint is

signal state: two_state_type;

signal stateB_entered_lastCycle: std_logic;

begin

process ( clk )

begin

if ( reset = '1' ) then

elsif ( rising_edge(clk) ) then

case state is

when stateA =>

if ( valid = '1' ) then

state <= stateB;

end if;

when stateB =>

when others =>

end case;

end if;

end process;

process(clk)

begin

if ( reset = '1' ) then

elsif ( clk = '1' ) then

case state is

when stateA =>

when stateB =>

stateB_entered_lastCycle <= '1';

when others =>

end case;

end if;

end process;

end behave;