I am new to the assembly language MIPS. I am studying how to implement new instructions to the set in MIPS. I get that there is no need for a "subi" instruction, we can do it by "addi" with a negative number hovewer, if we implement this new instruction how would we do it?

(This I-type instruction subtracts, using a sign-extended immediate value. subi $t2, $t7, 4)

Its RTL would look like this I assume:

IM[PC]

RF[rd] <- RF[rs] – RF[rt]

PC <- PC + 4

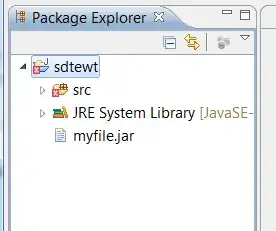

Now is the tricky part, how do i implement this instruction to this simplified MIPS architecture (see image below)? (By introducing new muxes/control signals etc, any way necessary)

Is there an inverter nodule which inverts the immediate value, so i can put it after sign extention, add a mux to chose between + and - and be done with it? Or it needs something else?