If you observe the MIPS 5-stage pipeline (1.Instruction Fetch - 2.Instruction Decode - 3.Execute - 4.Memory Access - 5.WriteBack), whether to branch or not is finally determined at Execute stage.

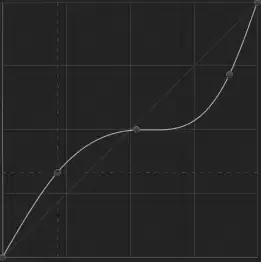

You can see in the image that the upper output of ALU is fed into a MUX to choose between normal PC step and branch.

Hence, when the CPU decides whether to branch, two pipeline stages have passed from the IF stage of corresponding instruction. Suppose PC1 = PC when IF and PC2 = PC when decides to branch. Hence PC2 = PC1+4. In order to revert PC2 to PC1+4, additional hardware is required. (for operation PC2-4)

In spite of this disadvantage, I wonder why does the MIPS processor uses PC+4 as base address rather than using PC+8 as it is?