I read about Static Hazard. We know Static 1-hazard is: Input change causes output to go from 1 to 0 to 1.

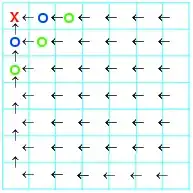

My note covers a Circuit as follows:

My notes says: When B=C=D=1, for any changes in A values, it's probable to have Static Hazard 1.

But I think:

for 1 to 0 transition of A static hazard 1 can be observed. for 0 to

1 transition of A no hazard can be observed.

anyone could describe my sentence is correct or my note say the correct sentence. which of them is correct ? why? Thanks.