I have the VHDL implementation that works on board, it detects the sequence 01110 and will raise a flag for 2 clock counts. It detects overlapping sequences as well where 011101110 would raise the flag twice.

I've checked my implementation with a logic analyzer on the board and am fairly confident that it works. I am feeding in a repetition sequence of 0111 at 10 kHz, on the board, it has a clock at 100 MHz where I scale it to 10 kHz with a prescaler.

My problem is, when trying to recreate a similar scenario using a simulation, I do not get any outputs as expected

Image from logic analyzer from board

Test Bench Code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity test_FSM_prac4 is

-- Port ( );

end test_FSM_prac4;

architecture Behavioral of test_FSM_prac4 is

component FSM_prac4 is

port (

inputSignal : in STD_LOGIC;

pushButton : in STD_LOGIC;

clk100mhz : in STD_LOGIC;

logic_analyzer : out STD_LOGIC_VECTOR (7 downto 0);

LEDs: out STD_LOGIC

); end component;

signal inputSignal : std_logic := '0';

signal pushButton: std_logic := '0';

signal clk100mhz: std_logic := '0';

signal logic_analyzer: std_logic_vector(7 downto 0);

signal LEDs : std_logic;

begin

uut : FSM_prac4 port map(

inputSignal => inputSignal,

pushButton => pushButton,

clk100mhz => clk100mhz,

logic_analyzer => logic_analyzer,

LEDs => LEDs

);

--generate clock 100mhz

clock_tic: process begin

loop

clk100mhz <= '0';

wait for 5ns;

clk100mhz <= '1';

wait for 5ns;

end loop;

end process;

input_changes: process begin

loop

inputSignal <= '0';

wait for 100us;

inputSignal <= '1';

wait for 100us;

inputSignal <= '1';

wait for 100us;

inputSignal <= '1';

wait for 100us;

end loop;

end process;

end Behavioral;

To show the mapping for logic Analyzer

logic_analyzer(0) <= masterReset;

logic_analyzer(1) <= newClock -- 10Khz Clock;

logic_analyzer(2) <= outputZ;

--FSM States

logic_analyzer(3) <= '1' when y = A ELSE '0';

logic_analyzer(4) <= '1' when y = B ELSE '0';

logic_analyzer(5) <= '1' when y = C ELSE '0';

logic_analyzer(6) <= '1' when y = D ELSE '0';

logic_analyzer(7) <= '1' when y = E ELSE '0';

If anyone could direct to what I am doing wrong on the test bench and how to replicate to get similar results as the first image as it shows that in simulation, it always stays at state A and the new clock is not toggling meaning that clk100mhz is somehow not connected but I can't figure out why.

Any help is greatly appreciated, thanks guys

edit:

I wrote a simple program to test my scalar clock

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity scaler_clk is

Port (

pushButton : in std_logic;

indicator : out std_logic;

clk100mhz : in STD_LOGIC;

clk10khz: out STD_LOGIC

);

end scaler_clk;

architecture Behavioral of scaler_clk is

signal clockScalers : std_logic_vector (12 downto 0):= (others => '0') ;

signal prescaler: std_logic_vector(12 downto 0) := "1001110001000";

signal newClock: std_logic := '0';

signal masterReset : std_logic;

begin

clk10khz <= newClock;

masterReset <= pushButton;

process (clk100mhz,masterReset) begin

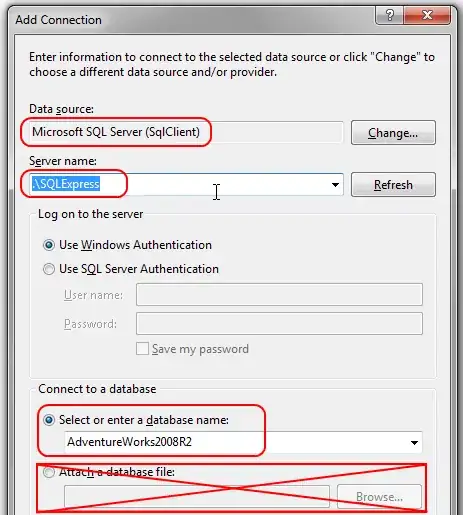

if(masterReset <= '1') then <--- error occurs here

clockScalers <= "0000000000000";

newClock <= '0';

indicator <= '1';

elsif (clk100mhz'event and clk100mhz = '1')then

indicator <= '0';

clockScalers <= clockScalers + 1;

if(clockScalers > prescaler) then

newClock <= not newClock;

clockScalers <= (others => '0');

end if;

end if;

end process;

end Behavioral;

test bench code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity test_scaler_clk is

-- Port ( );

end test_scaler_clk;

architecture Behavioral of test_scaler_clk is

component scaler_clk Port (

pushButton : in std_logic;

indicator : out std_logic;

--input clock

clk100mhz : in STD_LOGIC;

clk10khz: out STD_LOGIC

);end component;

signal clk100mhz: std_logic := '0';

signal clk10khz : std_logic;

signal pushButton: std_logic;

signal indicator : std_logic;

begin

uut: scaler_clk port map(

pushButton => pushButton,

indicator => indicator,

clk100mhz => clk100mhz,

clk10khz => clk10khz

);

pushButton <= '0';

clock_tic: process begin

loop

clk100mhz <= '0';

wait for 5ns;

clk100mhz <= '1';

wait for 5ns;

end loop;

end process;

end Behavioral;

Even though I set pushButton to '0', it is still triggering masterReset, anyone knows why, that's why the 10 kHz clock isn't working