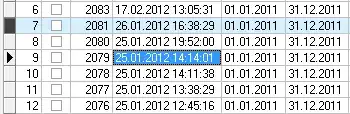

Here I have uploaded Simulation Result. In that at highlighted portion it should assign sys_clk to the both signal

I have written vhdl code to assign system clock(Sys_clk) after some delay on defined sclk_1 and sclk_2 signals.

When code run and executed, in simulation after 25 count of the counter, the status of these both signals simply show high (logic level high) instead of system Clock (Sys_Clk).

I'm using Artix 7 Basys -3 Board, and its having 100MHZ system Clock.

Can anyone help me how can I assign system clock (Sys_Clk) on defined signal ??

architecture Behavioral of Power_Sequence is

signal counter : integer := 0;

signal sclk_1 : std_logic := '0';

signal sclk_2 : std_logic := '0';

begin

process(Sys_Clk)

begin

if(Sys_Clk 'event and Sys_Clk = '1') then

if(resetb = '0')then

sclk_1 <= '0';

sclk_2 <= '0';

else

counter <= counter + 1;

if (counter > 24 and counter < 50) then

sclk_1 <= Sys_Clk;

sclk_2 <= Sys_Clk;

end if;

end if;

end if;

end process;

end Behavioral;