In Xilinx Vivado, I would like to buffer 8 independent AXI streams through a "AXI Virtual FIFO controller". From what I understand, the 8 streams must first be multiplexed into one stream using a "AXI4-Stream switch", and then demultiplexed using a second "AXI4-Stream switch".

The demultiplexing switch "axis_switch_0" uses the "tdest" signal to determine which Mxx_AXIS interface to send each transfer to. The "tdest" signal passes through the "AXI Virtual FIFO controller".

But I cannot figure out how to make the multiplexing switch "axis_switch_1" produce the "tdest" signal based on which Sxx_AXIS interface each transfer came from.

Any ideas?

EDIT

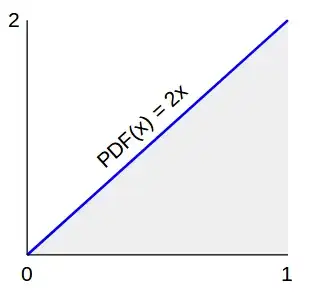

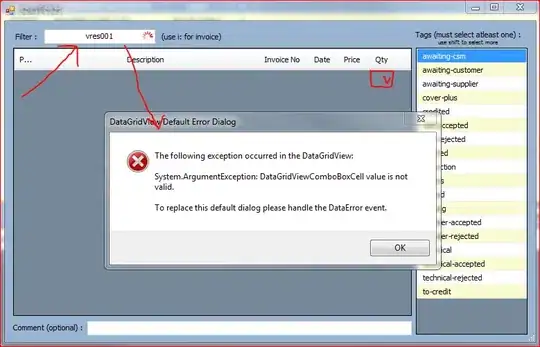

This is what happens if I enable TDEST or TUSER in "AXI4-Stream switch". No idea how 3bit TDEST/TUSER on the master interface becomes 24bits on the slave interfaces.