I'm having a problem with getting the desired output.

Here is my code:

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output reg [4:0] q

);

wire din3;

assign din3 = q[3] ^ q[0];

always @(posedge clk)

begin

if (reset)

q <= 5'd1;

else

q <= {q[0],din3,q[2],q[1],q[0]};

end

endmodule

This is the timing diagram of my output vs the correct output.

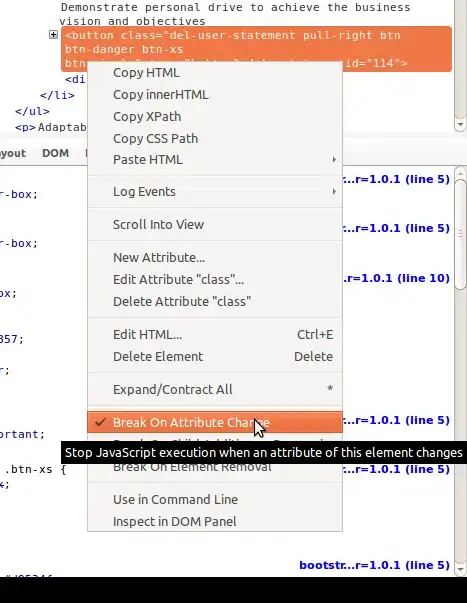

Also I keep getting this error:

Warning (13024): Output pins are stuck at VCC or GND

The Testbench code is not available to me because it's done behind the scenes on the HDLBits website.