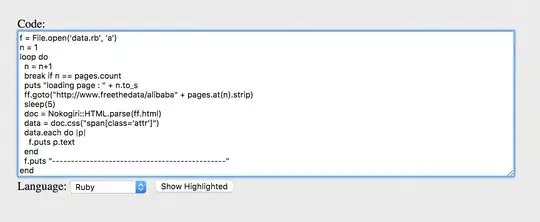

I am using Synopsys Design Compiler(SDC) for synthesis with compile_ultra. This option does advanced datapath extraction which basically tries to group(or chain) together as many arithmetic operations as possible and then uses carry-save arithmetic in order to efficiently implement this chain of operations. This is described in SDC user guide. The optimization supposedly leaves behind a description of the extracted datapath in binary files. I am pointing out these in the following screenshot. Is there a way to see what these files contain and figure out what datapath was finally produced by SDC ?

add_304_64_DP_OP_283_2056 is the name of the extracted datapath(as shown in the report_resources output at the beginning of the image). The corresponding had_unwound8_add_304_64_DP_OP_283_2056_0.a.e and had_unwound8_add_304_64_DP_OP_283_2056_0.b.e files are dumped by SDC.

Note: Cross posted from electronics stackexchange since it did not find enough purchase there.