I'm using active-hdl to simulate my FPGA designs and I'd like to know if it's possible to use dynamically generated strings to represent my signals in the simulator. For example, let's say I have a 4-bit std_logic_vector containing an op-code, I'd like the simulator to display the op-code strings "nop", "add", "sub" etc instead of the vector value.

I tried declaring a custom enumeration type at first but quickly discovered that you don't get to choose the values of the individual elements. My next solution was to use the enumeration for simulation display only and convert with a translation function:

type op_code_type is (nop, add, sub, unknown); -- not in order

signal op_code_str: op_code_type;

signal op_code: std_logic_vector(3 downto 0);

function to_string(op_code : std_logic_vector(3 downto 0))

return op_code_type is

begin

case op_code is

when "0000" => return nop;

when "0010" => return add;

when "0011" => return sub;

when others => return unknown;

end case;

end to_string;

begin

----- testbench -----

process

begin

op_code <= "0000";

wait for 1ns;

op_code <= "0001";

wait for 1ns;

op_code <= "0010";

wait for 1ns;

op_code <= "0011";

wait for 1ns;

end process;

op_code_str <= to_string(op_code);

end architecture;

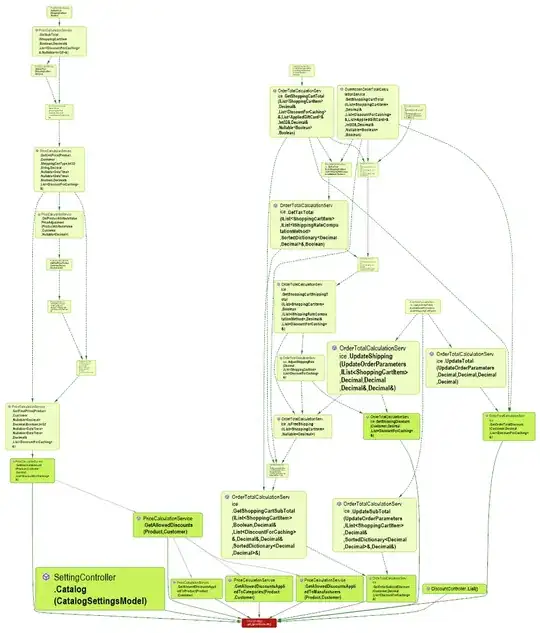

This actually works quite well, and is probably adequate for most things I want to do:

The main problem though is I'm stuck with string constants, so it'll be too impractical for more complex stuff like mov acc,x and all the many other variants a real-world design would have.

Are there ways to construct dynamic simulation identifiers like this? Or is it a fundamental limitation of HDLs?