I am a beginner in the development of FPGA. I am interested in how to correctly combine several modules in the top-level file.

For example: in the top-level file, I want to connect the output of module 1 to the input of module 2, and so on.

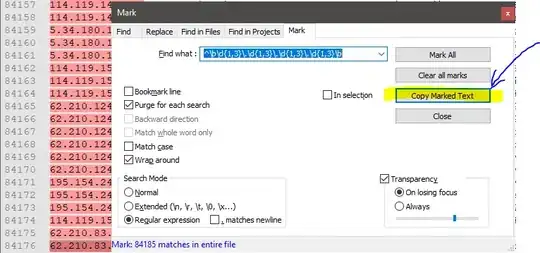

Please see the picture below:

I am trying to create a counter from 0 to 9 that outputs a number to a seven segment display. Please let me know if I'm doing something wrong or what could be improved.

Here is my code:

File "seven_segment" (top level):

module seven_segment (

input CLK,

output [6:0] out

);

counter counter ( .CLK(CLK));

bcd bcd ( .out(out));

endmodule

File "bcd":

module bcd (

input [3:0] in,

output reg [6:0] out

);

always @ (in) begin

case (in)

4'b0000 : out = 7'b1111110;

4'b0001 : out = 7'b0110000;

4'b0010 : out = 7'b1101101;

4'b0011 : out = 7'b1111001;

4'b0100 : out = 7'b0110011;

4'b0101 : out = 7'b1111011;

4'b0110 : out = 7'b1011111;

4'b0111 : out = 7'b1010000;

4'b1000 : out = 7'b1111111;

4'b1001 : out = 7'b1111011;

default : out = 7'b0000000;

endcase

end

endmodule

File "counter":

module counter (

input CLK,

output reg [3:0] count

);

always @ (posedge CLK)

begin

if (count == 4'b1010)

count <= 0;

else

count <= count + 1;

end

endmodule